Product Summary

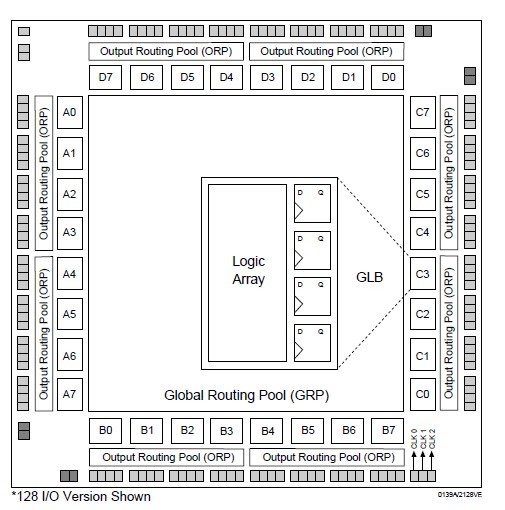

The ISPLSI2128VE100LT100 is a high density programmable logic device available in 128 and 64 I/O-pin versions. The ISPLSI2128VE100LT100 contains 128 registers, eight dedicated input pins, three dedicated clock input pins, two dedicated global oe input pins and a global routing pool (GRP). The GRP provides complete interconnectivity between all of these elements.

Parametrics

ISPLSI2128VE100LT100 absolute maximum ratings: (1)Supply voltage Vcc: -0.5 to +5.4V; (2)Input voltage applied: -0.5 to +5.6V; (3)Off-state output voltage applied: -0.5 to +5.6V; (4)Storage temperature: -65 to 150℃; (5)Case temp. with power applied: -55 to 125℃; (6)Max. junction temp. (TJ) with power applied:150℃.

Features

ISPLSI2128VE100LT100 features: (1)superfast high density in-system programmable logic; (2)3.3V low voltage 2128 architecture; (3)high performance ecmos technology; (4)in-system programmable; (5)100% IEEE 1149.1 boundary scan testable; (6)the ease of use and fast system speed of plds with the density and flexibility of fpgas; (7)lead-free package options.

Diagrams

|

ISPL1048E-50LQ. |

Other |

|

Data Sheet |

Negotiable |

|

||||||||

|

ispLSi 1016 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||

|

ispLSI 1016-110LJ |

Lattice |

CPLD - Complex Programmable Logic Devices USE ispMACH 4000V |

Data Sheet |

|

|

||||||||

|

ispLSI 1016-60LJ |

Lattice |

CPLD - Complex Programmable Logic Devices USE ispMACH 4000V |

Data Sheet |

|

|

||||||||

|

ispLSI 1016-60LJI |

Lattice |

CPLD - Complex Programmable Logic Devices USE ispMACH 4000V |

Data Sheet |

|

|

||||||||

|

ispLSI 1016-60LT44 |

Lattice |

CPLD - Complex Programmable Logic Devices USE ispMACH 4000V |

Data Sheet |

|

|

||||||||

(Hong Kong)

(Hong Kong)