Product Summary

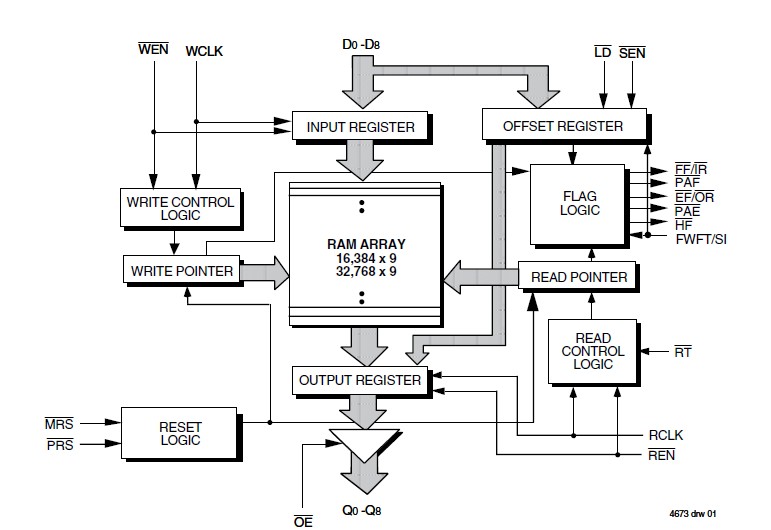

The IDT72V261LA10PFG is a kind of 3.3 VOLT CMOS SuperSync FIFO, which is functionally compatible versions of the IDT72261 designed to run off a 3.3V supply for very low power consumption. The IDT72V261LA10PFG is an exceptionally deep, high speed, CMOS First-In-First-Out (FIFO) memory with clocked read and write controls. The IDT72V261LA10PFG is particularly appropriate for network, video, telecommunications, data communications and other applications that need to buffer large amounts of data.

Parametrics

IDT72V261LA10PFG absolute maximum ratings: (1)VTERM, Terminal Voltage with respect to GND: –0.5 to +5 V; (2)TSTG, Storage Temperature: –55 to +125℃; (3)IOUT, DC Output Current: –50 to +50 mA.

Features

IDT72V261LA10PFG features: (1)Choose among the following memory organizations: IDT72V261LA: 16,384 x 9; (2)Pin-compatible with the IDT72V281/72V291 and IDT72V2101/ 72V2111SuperSync FIFOs; (3)Functionally compatible with the 5 Volt IDT72261/72271 family; (4)10ns read/write cycle time (6.5ns access time); (5)Fixed, low first word data latency time; (6)5V input tolerant; (7)Auto power down minimizes standby power consumption; (8)Master Reset clears entire FIFO; (9)Partial Reset clears data, but retains programmable settings; (10)Retransmit operation with fixed, low first word data; (11)latency time; (12)Empty, Full and Half-Full flags signal FIFO status; (13)Programmable Almost-Empty and Almost-Full flags, each flag can default to one of two preselected offsets; (14)Available in the 64-pin Thin Quad Flat Pack (TQFP) and the 64-pin Slim Thin Quad Flat Pack (STQFP); (15)High-performance submicron CMOS technology.

Diagrams

|

IDT7005 |

Other |

|

Data Sheet |

Negotiable |

|

||||||

|

IDT7005L |

Other |

|

Data Sheet |

Negotiable |

|

||||||

|

IDT7005L15J |

|

IC SRAM 64KBIT 15NS 68PLCC |

Data Sheet |

|

|

||||||

|

IDT7005L15J8 |

|

IC SRAM 64KBIT 15NS 68PLCC |

Data Sheet |

|

|

||||||

|

IDT7005L15JG |

|

IC SRAM 64KBIT 15NS 68PLCC |

Data Sheet |

|

|

||||||

|

IDT7005L15JG8 |

|

IC SRAM 64KBIT 15NS 68PLCC |

Data Sheet |

|

|

||||||

(Hong Kong)

(Hong Kong)