Product Summary

The IDT72V255LA10PFG is a 3.3 Volt CMOS SuperSync FIFO. The IDT72V255LA10PFG is functionally compatible versions of the IDT72V255LA10PFG designed to run off a 3.3V supply for very low power consumption. The IDT72V255LA10PFG is exceptionally deep, high speed, CMOS First-In-First-Out (FIFO) memories with clocked read and write controls.

Parametrics

IDT72V255LA10PFG absolute maximum ratings: (1)VTERM, Terminal Voltage with respect to GND:–0.5 to +5 V; (2)TSTG, Storage Temperature: –55 to +125℃; (3)IOUT, DC Output Current: –50 to +50 mA.

Features

IDT72V255LA10PFG features: (1)Pin-compatible with the IDT72V275/72V285 and IDT72V295/72V2105 SuperSync FIFOs; (2)Functionally compatible with the 5 Volt IDT72255/72265 family; (3)10ns read/write cycle time (6.5ns access time); (4)Fixed, low first word data latency time; (5)5V input tolerant; (6)Auto power down minimizes standby power consumption; (7)Master Reset clears entire FIFO; (8)Partial Reset clears data, but retains programmable settings; (9)Retransmit operation with fixed, low first word data latency time; (10)Empty, Full and Half-Full flags signal FIFO status; (11)Programmable Almost-Empty and Almost-Full flags, each flag can default to one of two preselected offsets; (12)Program partial flags by either serial or parallel means; (13)Select IDT Standard timing (using EF and FF flags) or First Word Fall Through timing (using OR and IR flags).

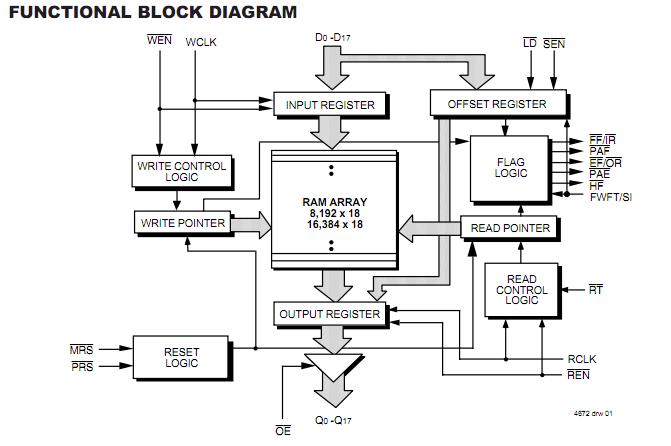

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

IDT72V255LA10PFG |

|

IC FIFO SS 8192X18 10NS 64-TQFP |

Data Sheet |

|

|

||||||

|

IDT72V255LA10PFG8 |

|

IC FIFO SS 8192X18 10NS 64-TQFP |

Data Sheet |

|

|

||||||

(Hong Kong)

(Hong Kong)