Product Summary

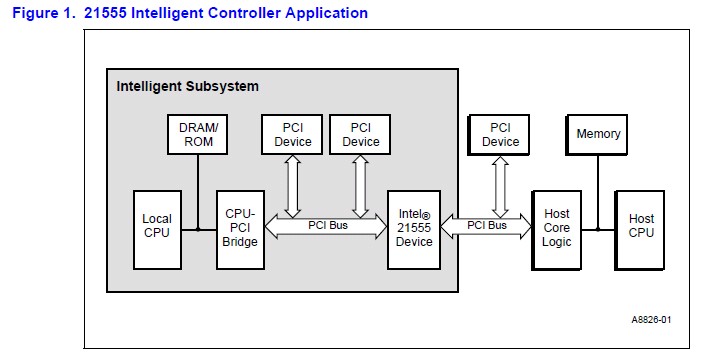

The FW21555BB is a PCI peripheral device that performs PCI bridging functions for embedded and intelligent I/O applications. The FW21555BB has a 64-bit primary interface, a 64-bit secondary interface, and 66-MHz capability. The 21554 a related PCI peripheral device, has a 64-bit primary interface, a 64-bit secondary interface, and 33-MHz capability. The FW21555BB is a non-transparent PCI-to-PCI bridge that acts as a gateway to an intelligent subsystem. It allows a local processor to independently configure and control the local subsystem. The FW21555BB implements an I2O message unit that enables any local processor to function as an intelligent I/O processor (IOP) in an I2O-capable system. Because the FW21555BB is architecture independent, it works with any host and local processors that support a PCI bus. This architecture independence enables vendors to leverage existing investments while moving products to PCI technology.

Parametrics

FW21555BB absolute maximum ratings: 1)Junction temperature, Tj: 125℃; (2)Supply voltage Vcc: 14.3 V; (3)Maximum voltage applied to signal pins: 15.5 V; (4)Maximum power, PWC: 13.0 W; (5)Storage temperature range, Tstg:–55℃ to 125℃.

Features

FW21555BB features: (1)3.3-V operation with 5.0-V tolerant I/O; (2)Selectable asynchronous or synchronous primary and secondary interface clocks; (3)Concurrent primary and secondary bus operation; (4)Fully compliant with the Advanced Configuration Power Interface (ACPI) specification; (5)Fully compliant with the PCI Bus Power Management specification; (6)Queuing of multiple transactions in either direction; (7)256 bytes of posted write (data and address) buffering in each direction; (8)256 bytes of read data buffering in each direction; (9)Four delayed transaction entries in each direction; (10)Two dedicated I2O delayed transaction entries; (11)Two sets of standard PCI Configuration registers corresponding to the primary and secondary interface; each set is accessible; (12)from either the primary or secondary interface; (13)Direct offset address translation for downstream memory and I/O transactions; (14)Hardware enable for secondary bus central functions; (15)IEEE Standard 1149.1 boundary-scan JTAG interface.

Diagrams

|

FW211 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||||||||||

|

FW21154AE |

Intel |

IC P-P BRIDGE 64BIT 33MHZ 304BGA |

Data Sheet |

|

|

||||||||||||||||||||

|

FW21154BE |

Intel |

IC P-P BRIDGE 64BIT 66MHZ 304BGA |

Data Sheet |

|

|

||||||||||||||||||||

|

FW213 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||||||||||

|

FW21555ABSL6G8 |

Intel |

IC BRIDGE P-P 64BIT 33MHZ 304BGA |

Data Sheet |

|

|

||||||||||||||||||||

|

FW216 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||||||||||

(Hong Kong)

(Hong Kong)