Product Summary

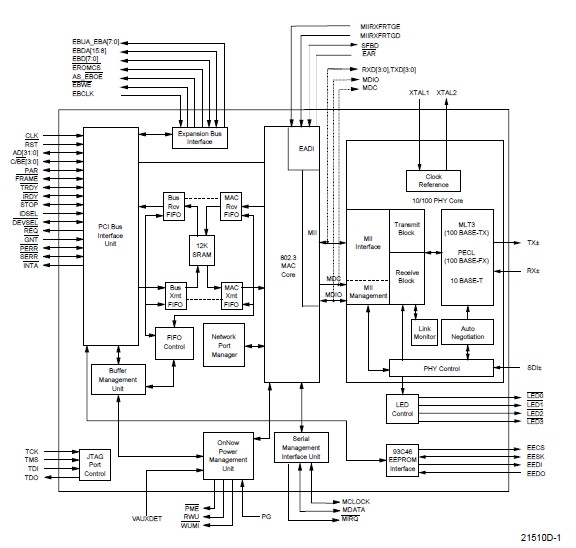

The AM79C973BVCW is a kind of single chip 32-bit full- duplex, 10/100-Megabit per second (Mbps) fully integrated PCI-to-Wire Fast Ethernet system solution, designed to address high-performance system application requirements. The AM79C973BVCW is a flexible bus mastering device that can be used in any application, including network-ready PCs and bridge/router designs. The bus master architecture provides high data throughput and low CPU and system bus utilization. The AM79C973BVCW is fabricated with advanced low-power 3.3-V CMOS process to provide low operating current for power sensitive applications.

Parametrics

AM79C973BVCW absolute maximum ratings: (1)Storage Temperature: –65°C to +150°C; (2)Ambient Temperature: -65°C to +70°C; (3)Supply voltage with respect to VSSB, VSS, DVSSD, DVSSP, and DVSSX: –0.3 V to 3.63 V.

Features

AM79C973BVCW features: (1)Single-chip PCI-to-Wire Fast Ethernet controller; (2)Fully Integrated 10/100 Mbps Physical Layer Interface (PHY); (3)Dual-speed CSMA/CD (10 Mbps and 100 Mbps); (4)Media Access Controller (MAC) compliant with IEEE/ANSI 802.3 and Blue Book Ethernet standards; (5)Supports PC98/PC99 and Wired for Management baseline specifications; (6)Serial Management Interface enables remote alerting of system management events; (7)Large independent internal TX and RX FIFOs; (8)EEPROM interface supports jumperless design and provides through-chip programming; (9)Supports up to 1 megabyte (Mbyte) optional Boot PROM and Flash for diskless node applications; (10)Extensive programmable internal/external loopback capabilities; (11)Extensive programmable LED status ; (12)Look-Ahead Packet Processing (LAPP) data handling technique reduces system overhead by allowing protocol analysis to begin before the end of a receive frame; (13)Includes Programmable Inter Packet Gap (IPG) to address less network aggressive MAC controllers; (14)Offers the Modified Back-Off algorithm to address the Ethernet Capture Effect; (15)IEEE 1149.1-compliant JTAG Boundary Scan test access port interface and NAND tree test mode for board-level production connectivity test; (16)Compatible with the existing PCnet Family driver/diagnostic software; (17)Software compatible with AMD PCnet Family and LANCE./C-LANCE. register and descriptor architecture; (18)Available in 160-pin PQFP and 176-pin TQFP packages; (19)Advanced +3.3 V CMOS process technology for low power operation applications.

Diagrams

|

Am79213 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

Am79231 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

Am79514 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

Am79533I |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

Am79534 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

Am79535 |

Other |

|

Data Sheet |

Negotiable |

|

||||

(Hong Kong)

(Hong Kong)